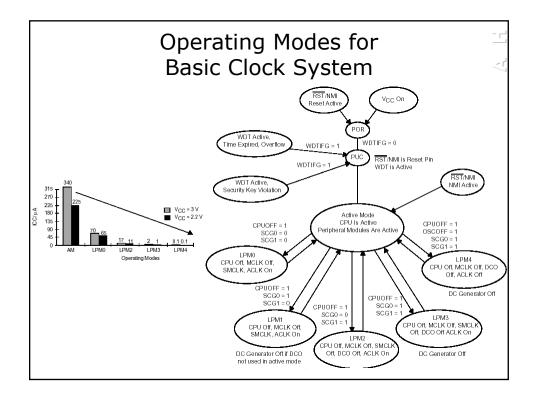

## Review: Operating Modes for Basic Clock System

| SCG1                                                                                                                                                  | SCG0 | OSCOFF | CPUOFF | Mode          | CPU and Clocks Status                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|---------------|------------------------------------------------------------------------------------|

| 0                                                                                                                                                     | 0    | 0      | 0      | Active        | CPU is active, all enabled clocks are active                                       |

| 0                                                                                                                                                     | 0    | 0      | 1      | LPM0          | CPU, MCLK are disabled<br>SMCLK , ACLK are active                                  |

| 0 1 0 1 LPM1 CPU, MCLK, DCO osc. are disabled<br>DC generator is disabled if the DCO is no<br>MCLK or SMCLK in active mode<br>SMCLK , ACLK are active |      |        |        |               |                                                                                    |

| 1 0 0 1 LPM2 CPU, MCLK, SMCLK, DCO osc. are di<br>DC generator remains enabled<br>ACLK is active                                                      |      |        |        |               |                                                                                    |

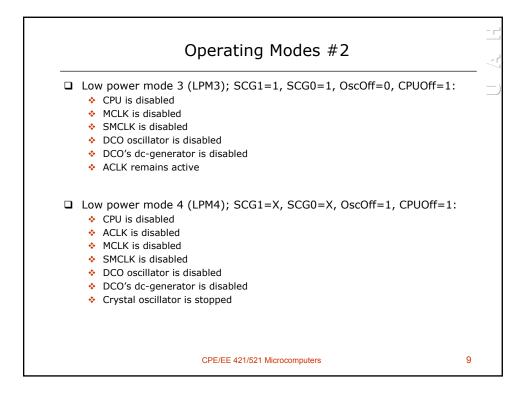

| 1                                                                                                                                                     | 1    | 0      | 1      | LPM3          | CPU, MCLK, SMCLK, DCO osc. are disabled<br>DC generator disabled<br>ACLK is active |

| 1                                                                                                                                                     | 1    | 1      | 1      | LPM4          | CPU and all clocks disabled                                                        |

| 1                                                                                                                                                     | 1    | 1      | 1      | LPM4          | ACLK is active                                                                     |

|                                                                                                                                                       |      |        | CPE    | /EE 421/521 I | Microcomputers 3                                                                   |

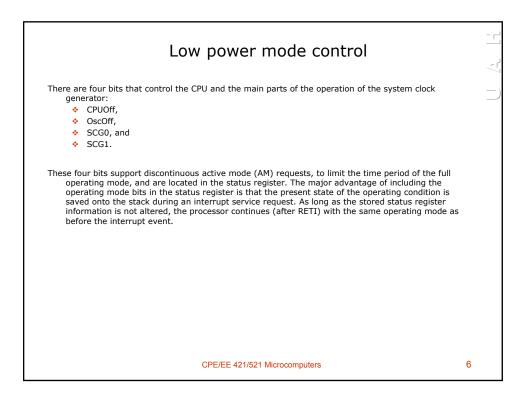

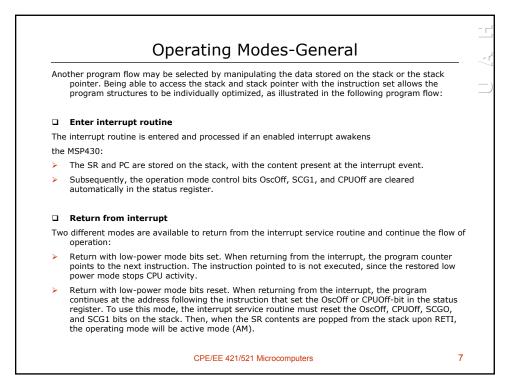

## **Operating Modes-General**

The MSP430 family was developed for ultralow-power applications and uses different levels of operating modes. The MSP430 operating modes, give advanced support to various requirements for ultralow power and ultralow energy consumption. This support is combined with an intelligent management of operations during the different module and CPU states. An interrupt event wakes the system from each of the various operating modes and the RETI instruction returns operation to the mode that was selected before the interrupt event.

The ultra-low power system design which uses complementary metal-oxide semiconductor (CMOS) technology, takes into account three different needs:

- $\hfill\square$   $\hfill$  The desire for speed and data throughput despite conflicting needs for ultra-low power

- Minimization of individual current consumption

- Limitation of the activity state to the minimum required by the use of low power modes

CPE/EE 421/521 Microcomputers

5

| Th | ere are six operating modes that the software can configure:                                                                                                                                                                                                                                                                      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Active mode AM; SCG1=0, SCG0=0, OscOff=0, CPUOff=0: CPU clocks are active                                                                                                                                                                                                                                                         |

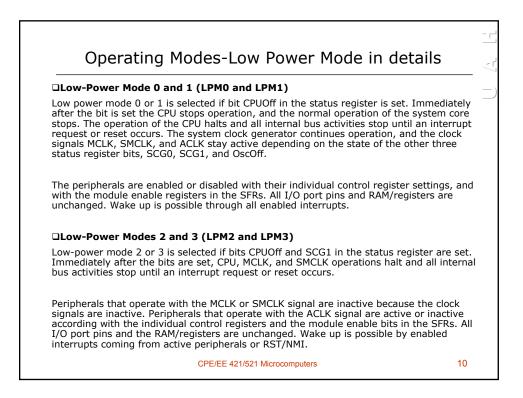

|    | Low power mode 0 (LPM0); SCG1=0, SCG0=0, OscOff=0, CPUOff=1:<br>CPU is disabled<br>MCLK is disabled<br>SMCLK and ACLK remain active                                                                                                                                                                                               |

|    | <ul> <li>Low power mode 1 (LPM1); SCG1=0, SCG0=1, OscOff=0, CPUOff=1:</li> <li>CPU is disabled</li> <li>MCLK is disabled</li> <li>DCO's dc generator is disabled if the DCO is not used for MCLK or SMCLK when in active mode. Otherwise, it remains enabled.</li> <li>SMCLK and ACLK remain active</li> </ul>                    |

|    | <ul> <li>Low power mode 2 (LPM2); SCG1=1, SCG0=0, OscOff=0, CPUOff=1:</li> <li>CPU is disabled</li> <li>MCLK is disabled</li> <li>SMCLK is disabled</li> <li>DCO oscillator automatically disabled because it is not needed for MCLK or SMCLK</li> <li>DCO's dc-generator remains enabled</li> <li>ACLK remains active</li> </ul> |

## <section-header><section-header><section-header><section-header><section-header><text><text><text><text>

| <pre>;===Main program flow with switch to CPUOff Mode====================================</pre>                                                                                                                                                                                                                                                                                                                                                                                     | □ The followin                                             | g example describes entering into low-power mode 0. |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------|--|--|--|

| <pre>;(CPUOff=1, GIE=1). The PC is incremented<br/>;during execution of this instruction and<br/>;points to the consecutive program step.<br/> ;The program continues here if the CPUOff<br/>;bit is reset during the interrupt service<br/>;routine. Otherwise, the PC retains its<br/>;value and the processor returns to LPMO.<br/><b>The following example describes clearing low-power mode 0.</b><br/>;===Interrupt service routine====================================</pre> |                                                            |                                                     |  |  |  |

| <pre>;during execution of this instruction and<br/>;points to the consecutive program step.<br/> ;The program continues here if the CPUOff<br/>;bit is reset during the interrupt service<br/>;routine. Otherwise, the PC retains its<br/>;value and the processor returns to LPMO.<br/><b>The following example describes clearing low-power mode 0.</b><br/>;===Interrupt service routine====================================</pre>                                               | BIS #18h,SR ;En                                            | ter LPM0 + enable general interrupt GIE             |  |  |  |

| <pre>;points to the consecutive program step.<br/> ;The program continues here if the CPUOff<br/>;bit is reset during the interrupt service<br/>;routine. Otherwise, the PC retains its<br/>;value and the processor returns to LPMO.<br/><b>The following example describes clearing low-power mode 0.</b><br/>;===Interrupt service routine====================================</pre>                                                                                             | ; (                                                        | CPUOff=1, GIE=1). The PC is incremented             |  |  |  |

| <pre> ;The program continues here if the CPUOff<br/>;bit is reset during the interrupt service<br/>;routine. Otherwise, the PC retains its<br/>;value and the processor returns to LPMO.<br/>The following example describes clearing low-power mode 0.<br/>;===Interrupt service routine====================================</pre>                                                                                                                                                 | ;d                                                         | uring execution of this instruction and             |  |  |  |

| <pre>;bit is reset during the interrupt service<br/>;routine. Otherwise, the PC retains its<br/>;value and the processor returns to LPMO.<br/><b>The following example describes clearing low-power mode 0.</b><br/>;===Interrupt service routine====================================</pre>                                                                                                                                                                                         | ;p                                                         | pints to the consecutive program step.              |  |  |  |

| <pre>;routine. Otherwise, the PC retains its<br/>;value and the processor returns to LPMO.<br/>The following example describes clearing low-power mode 0.<br/>;===Interrupt service routine====================================</pre>                                                                                                                                                                                                                                               | ;т                                                         | he program continues here if the CPUOff             |  |  |  |

| <pre>;value and the processor returns to LPMO.  The following example describes clearing low-power mode 0. ;===Interrupt service routine====================================</pre>                                                                                                                                                                                                                                                                                                  | ;b                                                         | it is reset during the interrupt service            |  |  |  |

| □ The following example describes clearing low-power mode 0.<br>;===Interrupt service routine====================================                                                                                                                                                                                                                                                                                                                                                   | ir                                                         |                                                     |  |  |  |

| <pre>;===Interrupt service routine====================================</pre>                                                                                                                                                                                                                                                                                                                                                                                                        | ;value and the processor returns to LPMO.                  |                                                     |  |  |  |

| <pre> ;CPU is active while handling interrupts BIC #10h,0(SP) ;Clears the CPUOff bit in the SR contents ;that were stored on the stack. RETI ;RETI restores the CPU to the active state ;because the SR values that are stored on ;the stack were manipulated. This occurs ;because the SR is pushed onto the stack ;upon an interrupt, then restored from the</pre>                                                                                                                | The following example describes clearing low-power mode 0. |                                                     |  |  |  |

| BIC #10h,0(SP) ;Clears the CPUOff bit in the SR contents<br>;that were stored on the stack.<br>RETI ;RETI restores the CPU to the active state<br>;because the SR values that are stored on<br>;the stack were manipulated. This occurs<br>;because the SR is pushed onto the stack<br>;upon an interrupt, then restored from the                                                                                                                                                   | ;===Interrupt s                                            | ervice routine====================================  |  |  |  |

| <pre>;that were stored on the stack. RETI ;RETI restores the CPU to the active state ;because the SR values that are stored on ;the stack were manipulated. This occurs ;because the SR is pushed onto the stack ;upon an interrupt, then restored from the</pre>                                                                                                                                                                                                                   |                                                            | ;CPU is active while handling interrupts            |  |  |  |

| RETI ;RETI restores the CPU to the active state<br>;because the SR values that are stored on<br>;the stack were manipulated. This occurs<br>;because the SR is pushed onto the stack<br>;upon an interrupt, then restored from the                                                                                                                                                                                                                                                  | BIC #10h,0(SP)                                             | ;Clears the CPUOff bit in the SR contents           |  |  |  |

| ;because the SR values that are stored on<br>;the stack were manipulated. This occurs<br>;because the SR is pushed onto the stack<br>;upon an interrupt, then restored from the                                                                                                                                                                                                                                                                                                     |                                                            | ;that were stored on the stack.                     |  |  |  |

| ;the stack were manipulated. This occurs<br>;because the SR is pushed onto the stack<br>;upon an interrupt, then restored from the                                                                                                                                                                                                                                                                                                                                                  | RETI                                                       | ;RETI restores the CPU to the active state          |  |  |  |

| ;because the SR is pushed onto the stack<br>;upon an interrupt, then restored from the                                                                                                                                                                                                                                                                                                                                                                                              |                                                            | ; because the SR values that are stored on          |  |  |  |

| ;upon an interrupt, then restored from the                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                            | ;the stack were manipulated. This occurs            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                            | ;because the SR is pushed onto the stack            |  |  |  |

| ;stack after the RETI instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                            | ;upon an interrupt, then restored from the          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                            | ;stack after the RETI instruction.                  |  |  |  |

|        | C – prog   | ramming msp430x14x.h       | •                                                                                 |

|--------|------------|----------------------------|-----------------------------------------------------------------------------------|

| * STAT | US REGIST  | ER BITS                    | #include "In430.h"                                                                |

| *****  | *******    | *********/                 |                                                                                   |

|        |            |                            | <pre>#define LPM0BIS_SR(LPM0_bits) /* Enter LP Mode 0 */</pre>                    |

| #defin | ne C       | 0x0001                     | #define LPM0_EXIT _BIC_SR(LPM0_bits) /* Exit LP Mode 0 */                         |

| #defin | ne Z       | 0x0002                     | #define LPM1BIS_SR(LPM1_bits) /* Enter LP Mode 1 */                               |

| #defin | ie N       | 0x0004                     | #define LPM1_EXIT _BIC_SR(LPM1_bits) /* Exit LP Mode 1 */                         |

| #defin | ie V       | 0x0100                     | #define LPM2BIS_SR(LPM2_bits) /* Enter LP Mode 2 */                               |

| #defin | ne GIE     | 0×0008                     | #define LPM2_EXIT _BIC_SR(LPM2_bits) /* Exit LP Mode 2 */                         |

| #defin | e CPUOFF   | 0x0010                     | <pre>#define LPM3BIS_SR(LPM3_bits) /* Enter LP Mode 3 */</pre>                    |

| #defin | ne OSCOFF  | 0x0020                     | #define LPM3_EXIT _BIC_SR(LPM3_bits) /* Exit LP Mode 3 */                         |

| #defin | ne SCGO    | 0x0040                     | <pre>#define LPM4BIS_SR(LPM4_bits) /* Enter LP Mode 4 */</pre>                    |

| #defin | ne SCG1    | 0×0080                     | #define LPM4_EXIT _BIC_SR(LPM4_bits) /* Exit LP Mode 4 */                         |

|        |            |                            | #endif /* End #defines for C */                                                   |

| /* Low | Power Mo   | des coded with             |                                                                                   |

| 1      | Bits 4-7 i | in SR */                   |                                                                                   |

| /* Beg | in #defin  | es for assembler */        |                                                                                   |

| #ifnde | efIAR_S    | YSTEMS_ICC                 | /* - in430.h -                                                                    |

| #defin | ne LPMO    | CPUOFF                     | Intrinsic functions for the MSP430                                                |

| #defin | ne LPM1    | SCG0+CPUOFF                | */                                                                                |

| #defin | he LPM2    | SCG1+CPUOFF                | unsigned short BIS SR(unsigned short);                                            |

| #defin | ne LPM3    | SCG1+SCG0+CPUOFF           | unsigned short _BIS_SR(unsigned short);<br>unsigned short BIC SR(unsigned short); |

|        | he LPM4    | SCG1+SCG0+OSCOFF+CPUOFF    | unsigned SHORT _BIC_SK(UNSigned SHORt)/                                           |

| /* End | l #defines | for assembler */           |                                                                                   |

| #else  | /* Begin   | #defines for C */          | 15 9 8 7 0                                                                        |

| #defin | he LPM0_bi | LS CPUOFF                  | OSC CPU                                                                           |

| #defin | he LPM1_bi | LS SCG0+CPUOFF             | Reserved V SCG1 SCG0 OFF OFF GIE N Z C                                            |

| #defin | ne LPM2_bi | LS SCG1+CPUOFF             |                                                                                   |

| #defin | he LPM3_bi | ts SCG1+SCG0+CPUOFF        |                                                                                   |

| #defin | ne LPM4_bi | LS SCG1+SCG0+OSCOFF+CPUOFF | rw-0                                                                              |

|        |            |                            | CPE/EE 421/521 Microcomputers 13                                                  |

|     | C Examples                                                                                                        |                       |                                         |          |  |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------|----------|--|--|--|--|--|

| //* | //***********************************                                                                             |                       |                                         |          |  |  |  |  |  |

| //  | // MSP-FET430P140 Demo BasicClock Output buffered #include <msp430x14x.n></msp430x14x.n>                          |                       |                                         |          |  |  |  |  |  |

| //  | // SMCLK, ACLK and MCLK                                                                                           |                       |                                         |          |  |  |  |  |  |

| //  | <pre>// Description; Output buffered MCLK, SMCLK and ACLK. void main(void)</pre>                                  |                       |                                         |          |  |  |  |  |  |

| //  |                                                                                                                   |                       |                                         |          |  |  |  |  |  |

| 11  | <pre>// //** XTAL'S REQUIRED - NOT INSTALLED ON FET **// // WDTCTL = WDTFW +WDTHOLD; // Stop Watchdog Timer</pre> |                       |                                         |          |  |  |  |  |  |

| 11  | MSP                                                                                                               | 430F149               | DCOCTL = DCO0 + DCO1 + DCO2; // Max DCO |          |  |  |  |  |  |

| 11  |                                                                                                                   |                       |                                         |          |  |  |  |  |  |

| //  | 71\1                                                                                                              | XIN -                 |                                         | Max Roll |  |  |  |  |  |

| //  | 1.1                                                                                                               | 32k                   | BCSCTL2  = SELS; // SMCLK = XT2         |          |  |  |  |  |  |

| //  | RST                                                                                                               | XOUT   -              | P5DIR  = 0x70; // P5.6,5,4 output       | uts      |  |  |  |  |  |

| //  | I                                                                                                                 | I                     | P5SEL  = 0x70; // P5.6,5,5 optic        | ons      |  |  |  |  |  |

| //  | I .                                                                                                               | XT2IN -               |                                         |          |  |  |  |  |  |

|     | 1                                                                                                                 | XTAL (455k - 8Mhz)    |                                         |          |  |  |  |  |  |

| 11  | RST                                                                                                               | XT20UT   -            | while(1)                                |          |  |  |  |  |  |

| 11  | 1                                                                                                                 | P5.4  >MCLK = DCO Max | {                                       |          |  |  |  |  |  |

| 11  | 1                                                                                                                 | P5.5 >SMCLK = XT2     | }                                       |          |  |  |  |  |  |

|     |                                                                                                                   | P5.6 >ACLK = 32kHz    | }                                       |          |  |  |  |  |  |

| 11  |                                                                                                                   |                       |                                         |          |  |  |  |  |  |

| 11  | M.Buccini                                                                                                         |                       |                                         |          |  |  |  |  |  |

| 11  | Texas Instruments                                                                                                 | , Inc                 |                                         |          |  |  |  |  |  |

| //  | January 2004                                                                                                      |                       |                                         |          |  |  |  |  |  |

| //  | // Updated for IAR Embedded Workbench Version: 2.21B                                                              |                       |                                         |          |  |  |  |  |  |

| //* | //*************************************                                                                           |                       |                                         |          |  |  |  |  |  |

|     | CPE/EE 421/521 Microcomputers 20                                                                                  |                       |                                         |          |  |  |  |  |  |

|      | C Examples                                          |                                                         |                                                   |                      |  |  |  |

|------|-----------------------------------------------------|---------------------------------------------------------|---------------------------------------------------|----------------------|--|--|--|

|      |                                                     |                                                         | •                                                 | $\overline{\langle}$ |  |  |  |

| 11   |                                                     | ) Demo - Timer_A Toggle Pl.0,<br>TSR. DCO SMCTA         | <pre>#include <msp430x14x.h></msp430x14x.h></pre> |                      |  |  |  |

|      |                                                     | coggle P1.0 using software and TA_0 ISR. Toggle rate is | s void main(void)                                 |                      |  |  |  |

| 11   |                                                     | CO/SMCLK cycles. Default DCO frequency used for TACLK   |                                                   |                      |  |  |  |

| //   | Durring the TA<br>added to                          | _0 ISR F0.1 is toggled and 50000 clock cycles are       | WDTCTL = WDTPW + WDTHOLD; // St                   | op WDT               |  |  |  |

| //   |                                                     | R is triggered exactly 50000 cycles. CPU is normally    |                                                   | .0 output            |  |  |  |

| - // | used only durn                                      | ing TA_ISR.                                             | CCTL0 = CCIE; // CCR0 interrupt ena               | pled                 |  |  |  |

|      | ACLK = n/a, MC                                      | LK = SMCLK = TACLK = DCO~ 800k                          | CCR0 = 50000;                                     |                      |  |  |  |

| 11   | TACTL = TASSEL_2 + MC_2; // SMCLK, contmode         |                                                         |                                                   |                      |  |  |  |

|      | // MSP430F149                                       |                                                         |                                                   |                      |  |  |  |

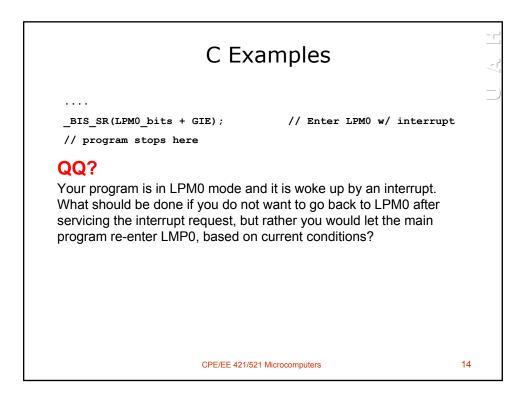

| 11   |                                                     |                                                         | _BIS_SR(LPM0_bits + GIE); // Enter LPM0 w/        | interrupt            |  |  |  |

| 11   | 71\1                                                | XIN   -                                                 | }                                                 |                      |  |  |  |

| - // | 1.1                                                 | 1                                                       |                                                   |                      |  |  |  |

| //   | RST                                                 | XOUT   -                                                | <pre>// Timer A0 interrupt service routine</pre>  |                      |  |  |  |

| //   | I                                                   | 1                                                       | interrupt[TIMERA0_VECTOR] void TimerA(void)       |                      |  |  |  |

| 11   | I                                                   | P1.0 >LED                                               | {                                                 |                      |  |  |  |

|      | M. Buccini                                          |                                                         | Plout $^= 0x01; // Toggle Pl.0$                   |                      |  |  |  |

|      | Texas Instrume                                      | CCR0 += 50000; // Add Offset to CCR0                    |                                                   |                      |  |  |  |

| 11   | // September 2003                                   |                                                         |                                                   |                      |  |  |  |

| - // | // Built with IAR Embedded Workbench Version: 1.26B |                                                         |                                                   |                      |  |  |  |

|      | // December 2003                                    |                                                         |                                                   |                      |  |  |  |

|      | -                                                   | R Embedded Workbench Version: 2.21B                     |                                                   |                      |  |  |  |

| //*  | *****                                               | ***************************************                 | *                                                 |                      |  |  |  |

|      | CPE/EE 421/521 Microcomputers 30                    |                                                         |                                                   |                      |  |  |  |